# PROFESSIONAL VERIFICATION

A Guide to Advanced Functional Verification

### **Paul Wilcox**

Cadence Design Systems, Inc.

# PROFESSIONAL VERIFICATION A Guide to Advanced Functional Verification

## PROFESSIONAL VERIFICATION A Guide to Advanced Functional Verification

PAUL WILCOX

Cadence Design Systems, Inc.

**KLUWER ACADEMIC PUBLISHERS**

NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW

eBook ISBN: 1-4020-7876-5 Print ISBN: 1-4020-7875-7

©2004 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

Print ©2004 Kluwer Academic Publishers Boston

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: http://kluweronline.com

and Kluwer's eBookstore at: http://ebooks.kluweronline.com

This book is dedicated to my wife, Elsa, for her unwavering love and support, and to my children, Jonathan and Elizabeth, for the inspiration and joy they have brought to my life.

### **Contents**

| Aut | Authors                                             |              |

|-----|-----------------------------------------------------|--------------|

| Ack | knowledgements                                      | XV           |

| Sec | tion 1 The Profession of Verification               |              |

| 1.  | INTRODUCTION                                        | 3            |

|     | LEARNING FROM OTHER'S BEST PRACTICES                | 4            |

|     | IS THIS BOOK FOR YOU?                               | 4            |

| 2.  | VERIFICATION CHALLENGES                             | 7            |

|     | MISSED BUGS—ARE WE JUST UNLUCKY?                    | 7            |

|     | THE NEED FOR SPEED                                  | 9            |

|     | DOING MORE WITH LESS                                | 10           |

|     | FRAGMENTED DEVELOPMENT, FRAGMENTED VERIFICATION     | <b>A-</b> 12 |

| 3.  | ADVANCED FUNTIONAL VERIFICATION                     | 15           |

|     | VERIFICATION AS A SEPARATE TASK                     | 15           |

|     | COORDINATING VERIFICATION WITH OTHER DEVELOPM TASKS | MENT<br>17   |

|     | VERIFICATION AS A MULTITHREADED PROCESS             | 18           |

|     | VERIFICATION IS NOT 100 PERCENT                     | 20           |

|     | VERIFICATION IS METHODOLOGY-BASED NOT TOOL-BASED    | 21           |

|     | VERIFICATION DIFFERS FOR EACH DESIGN                | 22           |

|     |                                                     |              |

| 4.  | SUCCESSFUL VERIFICATION                     | 23 |

|-----|---------------------------------------------|----|

|     | TIME MANAGEMENT                             | 23 |

|     | Start Early                                 | 23 |

|     | Remove Dependencies                         | 24 |

|     | Focus on Total Verification Time            | 24 |

|     | RESOURCE USAGE                              | 25 |

|     | Plan and Document                           | 25 |

|     | Build a Team                                | 26 |

|     | Use Someone Skilled in Management           | 26 |

|     | VERIFICATION PROCESSES                      | 27 |

|     | Choose the Right Tool for the Job           | 27 |

|     | Choose the Right Information for the Job    | 28 |

|     | Automate                                    | 28 |

|     | APPROACHES                                  | 29 |

|     | Keep Verification Real                      | 29 |

|     | Stress the Design                           | 30 |

| 5.  | PROFESSIONAL VERIFICATION                   | 31 |

|     | UNDERSTANDING PROFESSIONAL VERIFICATION     | 31 |

|     | THE VALUE OF VERIFICATION                   | 32 |

|     | THE COST OF ADVANCED VERIFICATION           | 33 |

|     | VERIFICATION: SECOND-CLASS CITIZEN          | 34 |

|     | The Perception of Verification              | 35 |

|     | Verification Training                       | 35 |

|     | CHANGING CURRENT PERCEPTIONS                | 36 |

|     | Develop the Profession of Verification      | 36 |

|     | Set Standards for Excellence                | 36 |

|     | Train and Develop Leaders                   | 37 |

|     | Share Best Practices                        | 37 |

| Sec | tion 2 The Unified Verification Methodology |    |

| 6.  | THE UNIFIED VERIFICATION METHODOLOGY        | 41 |

|     | WHAT MAKES A METHODOLOGY UNIFIED?           | 42 |

|     | IMPROVING SPEED AND EFFICIENCY              | 42 |

|     | KEY CONCEPTS                                | 43 |

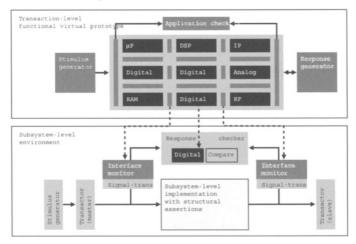

|     | Functional Virtual Prototype                | 43 |

|     | Transaction-Level Verification              | 46 |

*Contents* ix

|    | Unified Test Environment                      | 47 |

|----|-----------------------------------------------|----|

|    | Assertions                                    | 48 |

|    | Coverage                                      | 49 |

|    | Hardware Acceleration                         | 50 |

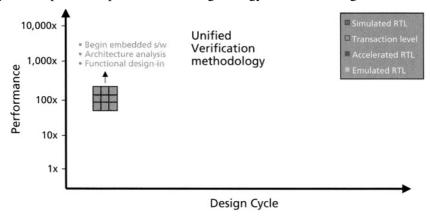

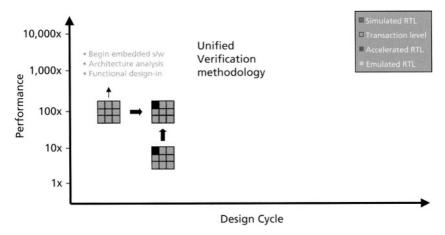

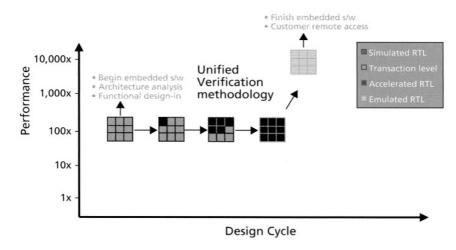

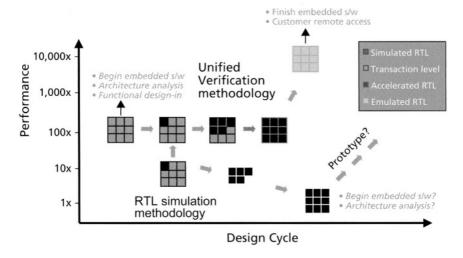

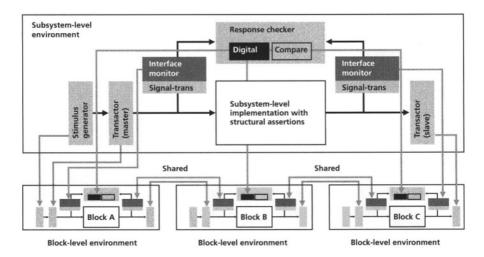

|    | METHODOLOGY OVERVIEW                          | 51 |

|    | Advantages of the UVM                         | 53 |

| 7. | UVM SYSTEM-LEVEL DESIGN                       | 57 |

|    | FROM WHITE BOARD TO FVP                       | 57 |

|    | An FVP versus a System Model                  | 58 |

|    | Costs and Benefits of an FVP                  | 59 |

|    | USING AN FVP                                  | 61 |

|    | Software Development                          | 62 |

|    | Subsystem Development                         | 63 |

|    | Design Chain Use                              | 63 |

|    | CREATING AN FVP                               | 64 |

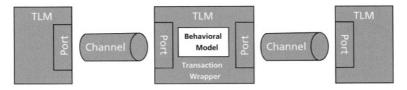

|    | Creating a Transaction-Level Model for an FVP | 64 |

|    | Creating a TLM from a Behavioral Model        | 64 |

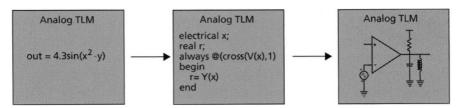

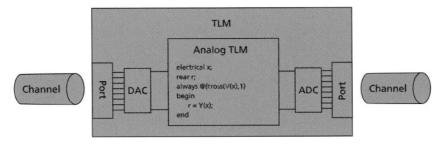

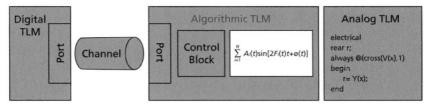

|    | Creating an Analog FVP TLM                    | 65 |

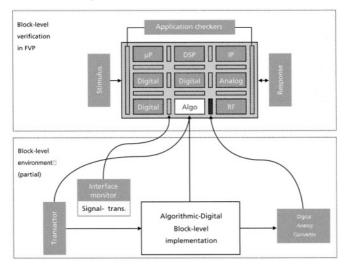

|    | Creating an Algorithmic Digital TLM           | 66 |

|    | Creating Stimulus and Response Generators     | 66 |

|    | Creating Interface Monitors                   | 66 |

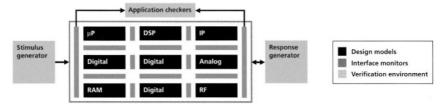

|    | Creating Architectural Checkers               | 67 |

|    | VERIFYING THE FVP                             | 67 |

|    | Stimulus Generation                           | 67 |

|    | Architectural Checks                          | 68 |

|    | Advanced Verification Techniques              | 69 |

| 8. | CONTROL DIGITAL SUBSYSTEMS                    | 71 |

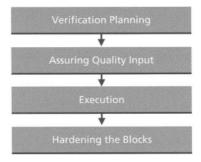

|    | STEP 1: VERIFICATION PLANNING                 | 72 |

|    | Goals and Objectives                          | 73 |

|    | Strategy                                      | 74 |

|    | Tactics                                       | 74 |

|    | Measurement and Analysis                      | 75 |

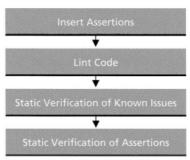

|    | STEP 2: ENSURING QUALITY INPUT                | 76 |

|    | Instrumenting with Assertions                 | 77 |

|    | Linting                                       | 78 |

|    | Static Verification of Known Issues           | 78 |

|    | Static Verification of Assertions             | 79 |

| Testbench Development Advanced Verification Techniques | 80<br>81<br>81 |

|--------------------------------------------------------|----------------|

| Advanced Verification Techniques                       | 81             |

|                                                        |                |

| Assertions in Simulation                               |                |

| Coverage                                               | 81             |

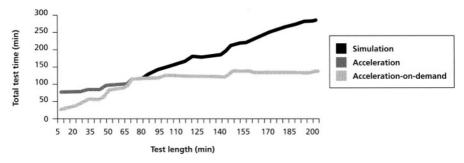

| Acceleration on Demand                                 | 82             |

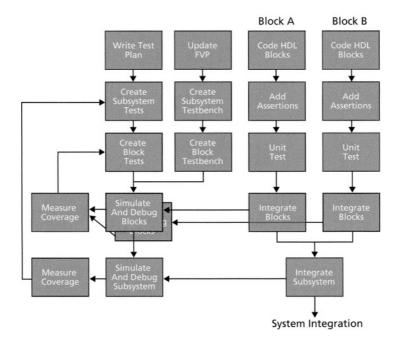

| Top-Down FVP-Based Flow                                | 83             |

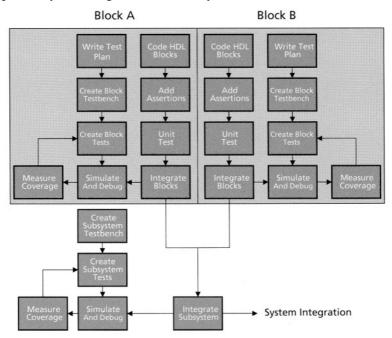

| Bottom-Up Specification-Based Flow                     | 84             |

| STEP 4: HARDENING THE BLOCKS                           | 86             |

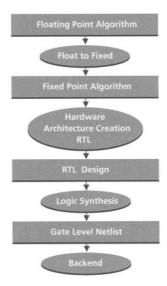

| 9. ALGORITHMIC DIGITAL SUBSYSTEMS                      | 87             |

| STEP 1: VERIFYING THE ALGORITHM                        | 88             |

| Algorithm Development in an FVP                        | 88             |

| Algorithmic Models                                     | 89             |

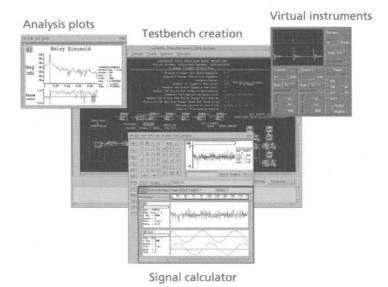

| STEP 2:TESTBENCH DEVELOPMENT                           | 90             |

| STEP 3: VERIFYING THE FINAL IMPLEMENTATION             | 91             |

| Advanced Verification Techniques                       | 92             |

| STEP 4: INTEGRATION AND DESIGN HARDENING               | 93             |

| 10. ANALOG/RF SUBSYSTEMS                               | 95             |

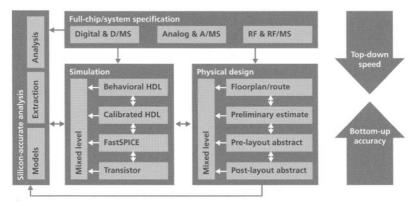

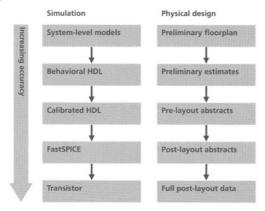

| CADENCE ACD METHODOLOGY                                | 95             |

| THE MEET-IN-THE-MIDDLE APPROACH                        | 97             |

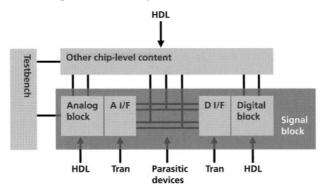

| THE ACD FLOW                                           | 100            |

| System Requirements                                    | 101            |

| Process Feasibility                                    | 101            |

| IC Requirements Translation                            | 101            |

| Simulation Strategy                                    | 102            |

| Behavioral-Level Top-Level Simulations                 | 104            |

| Block-Level Design                                     | 105            |

| Model Calibration                                      | 105            |

| Physical Design Strategy                               | 105            |

| Floorplan and Preliminary Top-Level Route              | 105<br>105     |

| Updated Routes RC Extraction                           | 103            |

| Silicon Analysis                                       | 106            |

| Chip Finishing                                         | 106            |

| 11. INTEGRATION AND SYSTEM VERIFICATION                | 107            |

| SYSTEM INTEGRATION                                     | 107            |

*Contents* xi

|      | Integrating a Subsystem into the FVP                   | 108 |

|------|--------------------------------------------------------|-----|

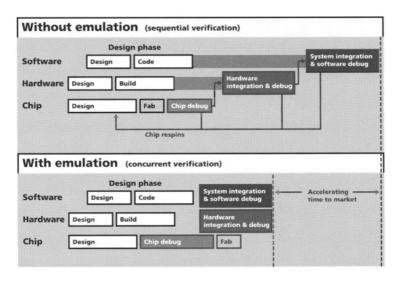

|      | Simulation Acceleration                                | 109 |

|      | Order of Integration                                   | 111 |

|      | SYSTEM VERIFICATION                                    | 111 |

|      | Software-based Simulation                              | 112 |

|      | Hardware Prototypes                                    | 113 |

|      | Emulation                                              | 113 |

| Sect | tion 3 Tools of the Trade                              |     |

| 12.  | SYSTEM-LEVEL DESIGN                                    | 119 |

|      | ISSUES ADDRESSED WITH AN FVP                           | 119 |

|      | VERIFICATION AND SOFTWARE DEVELOPMENT                  | 121 |

|      | Using the System Software Environment for Verification | 122 |

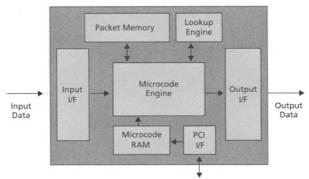

|      | Microcode Engines                                      | 122 |

|      | Hardware Platforms                                     | 123 |

|      | Software Algorithms                                    | 124 |

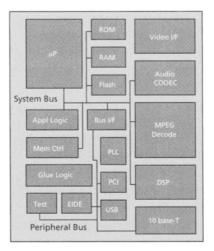

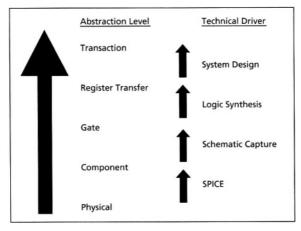

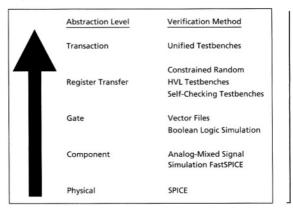

|      | ABSTRACTION                                            | 125 |

|      | Design Abstraction                                     | 125 |

|      | Verification Abstraction                               | 127 |

|      | Transaction-Level Modeling                             | 129 |

| 13.  | FORMAL VERIFICATION TOOLS                              | 131 |

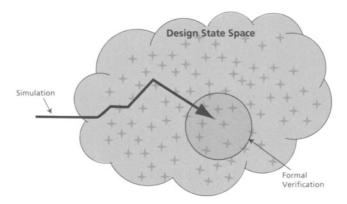

|      | WHEN TO USE FORMAL VERIFICATION                        | 131 |

|      | FORMAL VERIFICATION TECHNIQUES                         | 132 |

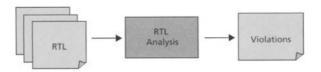

|      | RTL Analysis (Linting)                                 | 132 |

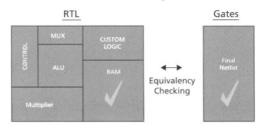

|      | Equivalency Checking                                   | 135 |

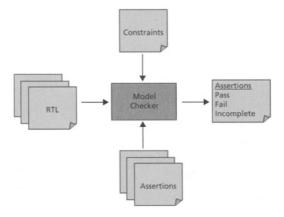

|      | Model Checkers                                         | 137 |

|      | Semi-Formal Verification                               | 138 |

| 14.  | TESTBENCH DEVELOPMENT                                  | 141 |

|      | TRADE-OFFS                                             | 141 |

|      | Reuse—Isolating Design-Specific Information            | 141 |

|      | Efficiency—Abstracting Design Information              | 142 |

|      | Flexibility—Using Standard Interfaces                  | 143 |

|      | Balancing Practical Concerns                           | 144 |

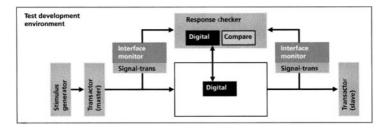

|      | Top-Down vs. Bottom-Up Testbench Development           | 145 |

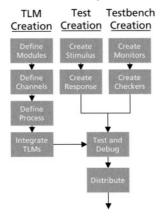

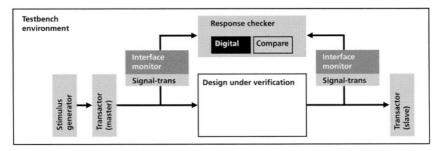

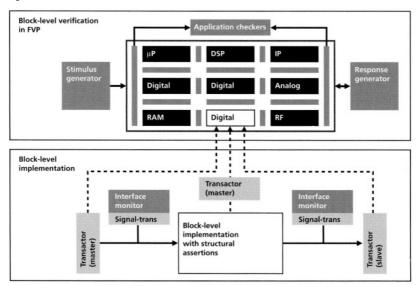

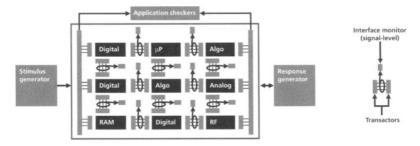

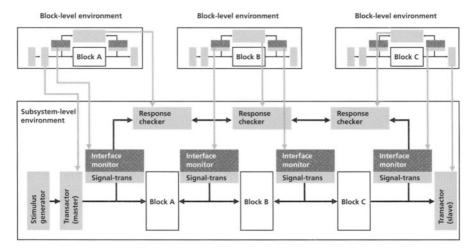

|      | UNIFIED TESTBENCHES                                    | 146 |

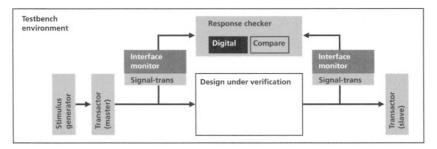

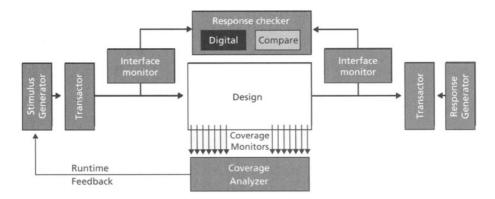

|      | Testbench Components                                   | 147 |

|       | Stimulus Generators                                        | 147 |

|-------|------------------------------------------------------------|-----|

|       | Transactors                                                | 147 |

|       | Interface Monitors                                         | 148 |

|       | Response Checkers                                          | 148 |

|       | Testbench API                                              | 149 |

|       | Top-Down Testbench Development                             | 149 |

|       | Bottom-Up Testbench Development                            | 151 |

|       | VERIFICATION TESTS                                         | 152 |

|       | Directed and Random Tests                                  | 153 |

|       | Types of Directed Tests                                    | 153 |

|       | Combining Random and Directed Approaches                   | 154 |

|       | Constraining Random Tests                                  | 155 |

|       | Testbench Requirements                                     | 156 |

| 15.   | ADVANCED TESTBENCHES                                       | 159 |

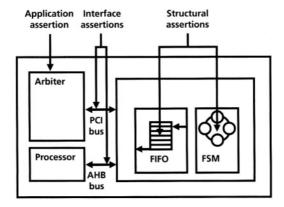

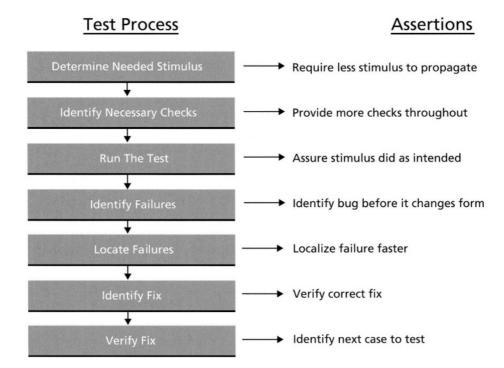

|       | ASSERTIONS                                                 | 159 |

|       | Using Assertions in the Test Process                       | 160 |

|       | Using Assertions                                           | 162 |

|       | Assertions and the FVP                                     | 164 |

|       | Assertions at the Block Level                              | 164 |

|       | Assertions and Chip-Level Verification                     | 165 |

|       | Assertions and System Verification                         | 165 |

|       | Flexibility and Reuse                                      | 166 |

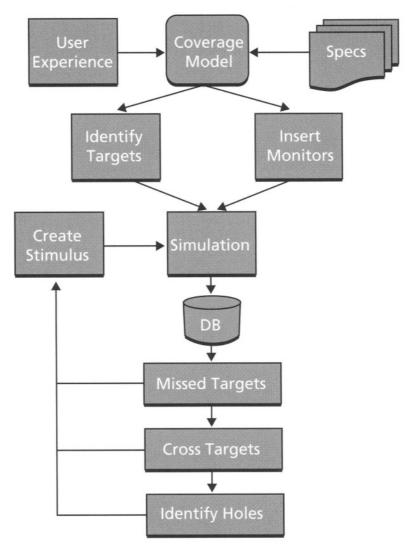

|       | COVERAGE                                                   | 166 |

|       | Using Coverage                                             | 167 |

|       | Filling Coverage Holes                                     | 170 |

|       | REACTIVE TESTBENCHES                                       | 171 |

| 16.   | HARDWARE-BASED VERIFICATION                                | 175 |

|       | ACCELERATED CO-VERIFICATION                                | 175 |

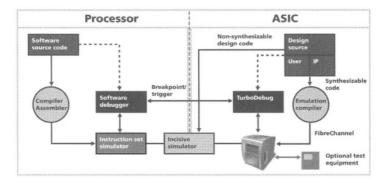

|       | Using an ISS, Software Simulator, and Accelerator/Emulator | 177 |

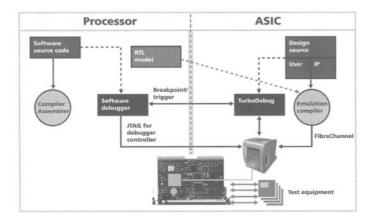

|       | Using an RTL Processor Model and Emulator                  | 178 |

|       | Using a Physical Model of the Processor and an Emulator    | 179 |

|       | Comparing Approaches                                       | 180 |

|       | INCORPORATING CO-VERIFICATION INTO YOUR DESIGN             |     |

|       | ENVIRONMENT                                                | 181 |

| Reso  | purces                                                     | 183 |

| Glos  | sary                                                       | 185 |

| Index | •                                                          | 189 |

|       |                                                            |     |

#### **Authors**

Paul Wilcox is the Director of Methodology Engineering at Cadence Design Systems, where he has worked since 2002. Previously, he worked at Cisco Systems, StratumOne Communications, 0-In Design Automation, and Sun Microsystems. He holds patents for work in advanced ASIC design and verification. Paul holds a Bachelor of Science degree in electrical engineering from Northeastern University and an MBA from San Jose State University.

Kurt Johnson is group director of Custom IC Marketing for Cadence Design Systems. At Cadence, Johnson has served with AMS Design Environment Services, where he established the AMS design environment from the ground up. He was also principal technical architect and strategist for full custom methodology services at Cadence IC Methodology Services. He has worked for Qualcomm, Western Digital, Teledyne Systems, and Motorola. Johnson earned his BSEE from Purdue University.

Ray Turner is the senior product line manager for Cadence's Incisive Palladium accelerator and in-circuit emulation systems, part of the Incisive Verification Platform. Before joining Cadence, he was the EDA marketing manager for P CAD products for seven years. Overall, Ray has 18 years experience in product management for EDA products. He also has 14 years experience in hardware, software, and IC design in the telecommunications, aerospace, ATE, and microprocessor industries. Ray received his Bachelor of Science degree in electrical engineering from Loyola University of Los Angeles. He holds patents for early work in digital signal processing and has authored two books on engineering.

#### Acknowledgements

Sir Isaac Newton once remarked, "If I have seen further [than certain other men], it is by standing upon the shoulders of giants." This book is based on the experiences and hard work of many giants in the design and verification of modern ICs. It would be impossible to list all the individuals who have contributed to the collected knowledge contained in this book, but it would be foolish to not acknowledge their contribution.

I have encountered many "giants" in my career who have taken the time and had the patience to teach me much of what is contained in this text. For that I would like to acknowledge the friends and co-workers I have worked with at Sun Microsystems, 0-In Design Automation, StratumOne Communications and Cisco Systems. Special thanks to Willis Hendly, David Kaffine, James Antonellis, Curtis Widdoes, and Richard Ho.

This book is the product of the efforts of many people at Cadence Design Systems, and I would like to acknowledge the following for their contributions and efforts in reviewing the text: Andreas Meyer, Grant Martin, Leonard Drucker, Neyaz Khan, Phu Huynh, Lisa Piper, and the entire Methodology Engineering team.

I want to acknowledge Linda Fogel for her tireless and professional editing, along with Kristen Willett, Kristin Lietzke, and Gloria Kreitman in Cadence's marketing communications group.

A special acknowledgement to Paul Estrada for providing me the opportunity and time to write this book and for showing faith in me when even I was ready to give up. One could not ask for a better mentor or friend.

Finally, I would like to acknowledge the true giants of my life, my parents, Eleanor and Gary Wilcox, for their love and support, and for teaching me the nobility of education.

# SECTION 1 THE PROFESSION OF VERIFICATION

#### Chapter 1

#### Introduction

Thinking about how it might not work

After years of doing what I considered grunt work in test, tool development, and verification, I finally got my chance to design a major portion of an important chip. I had created a detailed specification and beat all the scheduled milestones. My design was meeting its performance goals with time to spare, and the initial layout looked great. And then, two weeks before tapeout of the entire chip, the bug reports began to come in. The random verification regressions had been running fine for weeks until some of the parameters were loosened. Suddenly, my block was losing or misordering transactions, and all the simulations were failing. I found what I thought was a one-in-a-million corner case bug, but the next day the simulations were failing again. Another fix and another fix and still the bugs kept popping up. I was called in by the project managers. The tapeout deadline was at risk of slipping and it was because of me.

As I drove home that night, I tried to figure out what was going wrong. I had followed all the design rules, creating a very complex design in smaller size and greater performance than had been required. The data structure I had come up with could support many advanced features, and we were even patenting it. As I thought about it, I saw that the complexity I had added also created many new possible side effects, and the simple testbench I had written could not test these side effects. I realized that the only way I could get this design back on track was to stop thinking about how it should work and start thinking about how it might not work. It was at this moment that I began to understand functional verification.

But I'm not alone in going through this. Most engineers throughout the integrated circuit (IC) industry have had similar experiences. Fortunately, functional verification is evolving from an afterthought to an integral part of the development process. The evolution has occurred not because of forethought and careful planning, but out of necessity. Functional verification teams must keep up with growing complexities, growing device sizes, rapidly changing standards, increased performance demands, and the rapid integration of separate functions into single systems. Functional verification of today's nanometer-scale, complex ICs requires professional verification.

This book explores professional verification in a practical manner by detailing the best practices used by advanced functional verification teams throughout the industry. The goal of this book is not to present research into

new areas of verification or to provide a how-to manual for a specific tool or language. Instead, this book describes the advanced verification process based on what real teams are doing today so that you can incorporate this information into your own work.

#### LEARNING FROM OTHER'S BEST PRACTICES

Anyone who is even indirectly associated with the development of advanced ICs today is well aware of the numerous issues surrounding functional verification. Larger designs with increasing complexity and shorter development cycles have made yesterday's basic verification techniques unusable. While verification teams struggle with doing more verification to ensure higher quality and first past success, they are faced with fewer resources and outdated tools. Functional verification is a moving target for many teams who feel they are going to battle unprepared and understaffed.

Where can verification teams go to address the issues they face day in and day out? Most new research in verification focuses on mathematical techniques or system-level approaches that require major changes in verification as well as design and infrastructure. Engineering schools generally do not include functional verification in their curriculums. The only place to turn to for guidance is to other verification teams. By studying the best practices of advanced verification teams and learning from their successes and failures, engineers can gain valuable insights for addressing their own verification needs.

There is no perfect verification team in the industry today, and no two teams face the same set of issues. Therefore, it is important to examine the best practices of a wide variety of teams to glean the issues most important to you. Cadence Design Systems works with and studies the practices of the most advanced verification teams. This book is based on these collected experiences. It provides a wide array of knowledge and practices that you can use to address your specific concerns.

#### IS THIS BOOK FOR YOU?

If you are a researcher or an engineering student, this book offers a useful presentation of the advanced techniques used by today's successful verification teams. However, the book assumes some basic knowledge in the known issues and processes used in industry today. A list of excellent resources on

the fundamentals and techniques of functional verification is provided in Appendix A, "Resources."

If you are a project manager who oversees IC development, you will find the information on methodology and process improvements valuable. If you are an architect, system designer, system integrator, software developer, or tool developer, you might not consider verification a primary concern. But gaining a good understanding of the overall verification process and how that process can be integrated into your own area of expertise could be beneficial. Often design engineers verify their own block or another designer's block. Many of today's register-transfer level (RTL) designers understand the importance of functional verification and the role it plays in the development process. This book provides information on advanced verification that you can use in your job as you move through your career.

But the main audience for this book is the verification engineer. You are the professionals who face the day-to-day responsibilities and challenges of verifying the largest and most advanced ICs today. This book is an invaluable resource for understanding the complete verification process and how advanced teams throughout the industry successfully attain their goals.

This book focuses on the practical application of advanced verification techniques using today's best practices. The first section presents some of the fundamental topics in verification today and discusses the profession of verification. The second section shows how verification issues can be addressed, and shows how all of the practices fit together to form a complete unified methodology. The final section provides an in-depth look at many of the topics discussed in the second section.

#### Chapter 2

#### **Verification Challenges**

Missed bugs, lack of time, and limited resources

Every development team faces verification issues of some kind. Some might be due to the size or number of designs, some to the complexity of the design, some to the verification process being used. Verification teams continually attempt to address these issues only to find that new problems arise that are more complex than the original ones. Almost every issue in verification today can be placed in one of three buckets: missed bugs, lack of time, or lack of resources. The most pressing issue is the inability to find all the bugs during the verification process. Given enough time and resources, teams can verify with a high degree of confidence that a design will work. But having enough time to complete verification is a challenge. So more resources, more compute power, and more processes are thrown at the problem in hopes of decreasing the time to complete successful verification. Yet resources are expensive, which leads to the perception that verification takes too many resources to be successful on time. Teams need to find all the bugs in the shortest amount of time, with the fewest number of resources, in the most efficient and effective manner. Let's take a closer look at each of these areas.

#### MISSED BUGS—ARE WE JUST UNLUCKY?

The highest priority for verification teams has always been to find bugs. All the effort placed in architecture, design, implementation, and verification can be wasted with one missed functional bug. The farther down the supply chain a bug is found, the more costly it is to everyone involved. You can determine a company's belief in their design and verification processes by examining the number of planned spins they account for in their schedules and budgets. Some teams automatically plan and budget with the assumption that a certain number of functional bugs will not be found in verification. Other teams plan for first-pass success, and respins are only part of the contingency plan and budget.

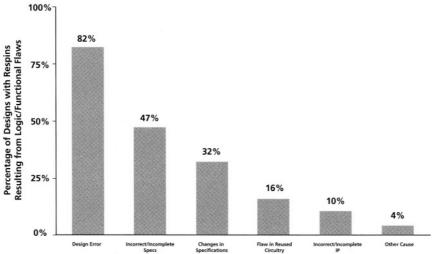

It does not matter how fast or advanced your process is if bugs slip through into silicon, causing the project to be delayed or cancelled. A recent study by Collette International Research of IC/ASIC designs and functional verification issues related to chip design found that the most common sources of functional bugs found in silicon are design errors, incorrect or incomplete

specifications, and changing specifications.<sup>1</sup> Each of these problems can be addressed with better use of tools and verification processes. Designer errors can range from simple typographical errors to incorrect implementations of complex functions or features. Using tools targeted at improving code quality and testbenches that thoroughly stimulate and check the design can increase the chance of finding these bugs. Incomplete or incorrect specifications are due to a lack of process and discipline in the development process. Verification can address this problem by requiring an executable specification and implementing detailed review processes. Miscommunication errors most often occur when parts of a design developed by different engineers or teams are integrated together. Verification can remedy this with thorough integration and system testing.

Causes of IC/ASIC Logic/Functional Flaws

Figure 1. Reasons for Missed Bugs from the Collette Study

Every project seems to encounter one or two "one in a million" bugs. No matter how thorough the verification process is, it is impossible to know about and verify every possible scenario. Inevitably, a bug is found in the lab that seems so obscure, requiring an unthinkable number of events to occur in just such a sequence. Engineers console themselves by thinking that there is no way they could have thought of that bug ever occurring. But when two or

<sup>1.</sup>Collett International Research, Inc., 2002 IC/ASIC Functional Verification Study, North America.

three of these "one in a million" bugs are found in every project, a solution needs to be found.

The difficulty in finding obscure bugs in large designs is that there are more possible scenarios than there is time to test. Verification teams attempt to address these bugs using advanced automated techniques, such as formal verification or constrained random testbenches. Automating the processes increases the likelihood that the correct sequence of events to stimulate and catch the bug occur. But like any bug, finding obscure bugs is best handled by using new or better tools and processes.

#### THE NEED FOR SPEED

Time-to-market pressures have forced the entire IC development process to be completed in less time, while the size and complexity of designs continue to increase. Many verification teams are challenged by completing the verification process on time.

Probably the most asked question by development teams is "when are we done?" Verifying large complex designs is an exercise in risk management. If you stop and tape out too soon, you risk finding a bug in silicon. If you wait and tape out too late, you may have wasted an opportunity to get to market sooner. There is no easy answer to determining when you have done enough verification, and often the answer is different for each design. Teams have attempted to use metrics, such as bug rate or coverage, but they do not always provide accurate enough information. Teams often determine when they are done based on a mix of experience, metrics, and gut feel.

Teams may not be able to determine when they are done, but they usually know when they are not. Every team has a feel for what testing must be done before a design is ready to tape out. It is not until they reach the point that they have tested everything that they can think of that determining completeness becomes an issue. Often teams never reach this point due to schedule constraints—no need to address determining when you are done if you know there is testing still to complete. This issue often boils down to a need for verification speed. If teams are able to verify what they know needs to be tested as fast as possible, they will then have time to analyze metrics and make a thorough conclusion on completeness before the clock runs out.

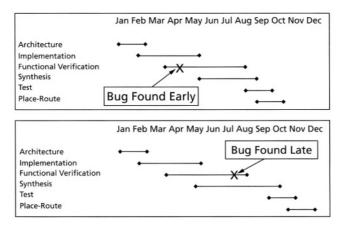

Finding easy or obvious bugs late in the verification process is very frustrating. Having a functionally correct design is a prerequisite for many development processes, such as synthesis, software development, and system verification. Finding a bug late often means resetting these processes, as shown Figure 2. Obviously, the earlier bugs are found the better, but finding

bugs sooner is only a benefit if it decreases the total verification time. Some techniques take so long to debug or to reverify that the total verification time is the same or worse.

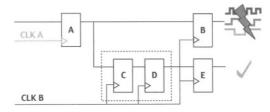

Figure 2. Late State Bugs Delay Project

Finding 98 percent of the bugs in a design is just a matter of using a methodical process. Finding the last 2 percent, however, often takes the most time and effort. Finding tough bugs is considered partly an art, partly luck, and a lot of hard work. Having engineers experienced in debugging is always helpful, but it still takes a lot of hard work. Tough bugs are hard to find because of misconceptions, because they involve a large amount of the design, and because they require many simulation cycles to find and recreate. Designers or debuggers often have misconceptions about the operation of the design, so they might not be focusing on the real cause. When debugging complex designs, the bug seems to move throughout the design—it starts in one block, is traced to another and another, until it is found in a place nobody would have thought to look. Once an incorrect operation is identified, it might take many more cycles to recreate the bug using the correct debug tools.

#### DOING MORE WITH LESS

Given enough time and resources most advanced verification teams can reach their goals. But time and resources are valuable commodities. Verification teams need to reach their goals in less time with the least amount of resources possible.

The verification process requires many resources, including engineers. Finding experienced verification engineers is difficult. Currently, schools do

not offer formal training in verification, so teams are left with trying to hire experienced engineers or training inexperienced engineers. This often leads to specialized verification engineers who know how to perform some verification tasks, but not all. Specialized resources can only be utilized on specific tasks, so unless the process is managed very carefully, resources are not utilized to their fullest extent. The net effect is inefficiencies in the verification process, limiting the amount of work that can be done.

Verification resources also include compute power and verification tools. In the past, many teams have attempted to throw compute power at verification to get it done faster. Today, computer and networking hardware is relatively cheap, but outfitting a large server farm with the necessary software licenses and verification tools can be costly. Quite often verification tools focus on one specialized task in the process and can only be used for a small percentage of the overall project time. Outfitting a server farm with software to meet the demands for this limited amount of time can be very costly.

A mantra of many good code developers is "write once and use often." Unfortunately, the mantra in verification seems to be "write often and use once." Time is often wasted capturing and replicating the same information multiple times for different processes and tools. Different environments require the same information but in different representations. The goal of verification teams should be to reuse the information from task to task and from project to project. Verification reuse can provide a huge productivity gain if done correctly. Making models and components reusable requires more time and effort, but if this is amortized across multiple projects, it is often worth the effort and costs. Verification teams need to identify when reuse is applicable and have the processes and methodology in place for utilizing components or models multiple times. If teams do not plan for reuse, the work can be wasted.

Reusing design blocks is prevalent today in large complex designs. It is often easier to reuse or modify a block from a previous design than to design a block from scratch. Unfortunately, the verification for that block may have been done by a different team using different methods and environments than your team plans to use. Do you trust that the design was verified correctly the first time? Does the design need to work differently in your system? These questions often lead development teams to reverify existing blocks to reduce the risk of failure.

Development teams want to be able to reuse old design blocks without having to reverify the old design. This requires design teams to design blocks that work for the intended design as well as newer designs. Verification teams need to develop environments that can quickly reverify existing designs when they change and that can also expand to verify designs within different system

environments. The gain in efficiency design teams realize from reusing design IP needs to be met with an equal focus on efficiency in the verification process.

### FRAGMENTED DEVELOPMENT, FRAGMENTED VERIFICATION

Whether the verification issue is related to missed bugs, speed, or efficiency, addressing the problem involves careful analysis and proper execution of the solution. Problems involving missed bugs are usually related to not using the correct tool or technique or using them incorrectly. These types of problems are often resolved by understanding the root cause of the problem and then selecting the correct technique to address it. The third section of this book discusses different verification techniques and how they can be used to address these types of issues.

Addressing issues of speed and efficiency, however, is not as straightforward as addressing missed bugs. Fragmentation in the verification process is the major cause of lost speed and efficiency. Today's verification process is fragmented into many isolated stages that do not share information or common techniques. This fragmentation results in duplicated processes, incompatible techniques, and lost time.

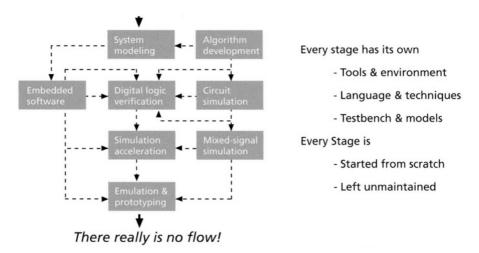

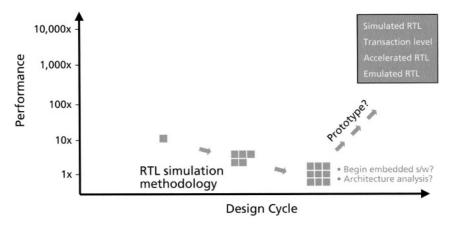

Figure 3. Typical Verification Flow

If we look at a typical verification flow, the fragmentation is obvious. Each task has its own stage with its own tools, environment, user interface, and models. Reuse from task to task, often known as vertical reuse, is limited or impossible. The same information is recreated at each stage, only to be left unmaintained once the task is completed. This "information rot" makes it nearly impossible to quickly make late changes in the design and rerun the task.

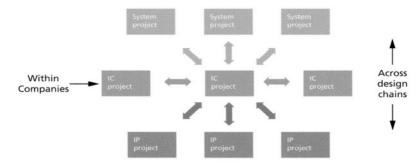

Fragmentation also exists from project to project. Few companies have a common verification flow for all projects. Even derivative projects often require new verification flows to be developed. Because each project is different, reusing models or information is impossible. Even though design IP can be reused from project to project, verification IP used to reverify the design often cannot be reused. Fragmentation also exists between design chain partners. Designs today are linked in a chain with IP developers providing blocks to IC developers, who provide devices to system developers. Fragmentation between design chain partners results in recreating verification environments at each stage in the design chain.

Verification environments & verification IP not reused

Figure 4. Fragmentation Across the Design Chain

The verification process has also become fragmented due to the ad hoc approach most teams use to develop their process. Instead of addressing the verification process as a whole, teams address individual issues on an asneeded basis. Teams add new techniques or tools without regard for the overall process, resulting in a flow that resembles islands of automation. With the advent of hardware description languages (HDL) and common implementation flows, the productivity of design teams has surpassed the ability for verification teams to keep up. Verification teams, who are under great time and resource pressure, end up just fighting fires and not addressing long-term issues, which results in fragmented approaches to verification.

No single tool or method can address the fragmentation in your development process. In fact, they might make it worse. What is needed is a methodology to unify all the stages, from system design to system design-in, across different design domains and projects. Only by unifying the entire verification process will fragmentation be removed, making dramatic gains in speed and efficiency possible.

The second section of this book looks at a unified verification methodology that is based on best practices used by advanced verification teams today. It gives you a view into how the different tools and techniques can be used together to address today's major verification challenges. But first, let's look at the role advanced functional verification plays in developing a unified verification methodology.

#### Chapter 3

#### **Advanced Funtional Verification**

Viewing verification differently

Advanced functional verification is not simply doing more of what you are already doing or using more powerful tools to make your job easier. Advanced functional verification is a fundamentally different way of thinking about and performing verification of large complex designs. Let's look at some of the basic principles of advanced functional verification and the implications these principles have in verification today.

#### VERIFICATION AS A SEPARATE TASK

For many years, verification was considered part of the design process. The verification strategy was developed by the design team, and verification was performed after the code was completed, usually by the designer who wrote it. This approach worked for small designs, where verification made up only a small percentage of the total project time. As the size of designs grew and the complexity increased, verification became a much larger portion of the total development effort. Advanced development teams realized that they had to treat verification as an independent development task.

Separating the verification of a design from the development of the design helps improve the efficiency of the process and the quality of the results. Today's large designs often require multiple complex testbenches and several layers of integration. Waiting until the design is complete to begin the verification process increases the total development time. By making the verification process independent, verification can begin in parallel with the design process. Instead of waiting for testbenches to be created and tests to be written after the design is completed, a parallel verification process enables the development team to begin testing the design immediately after it has been developed.

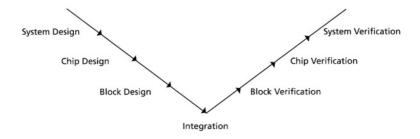

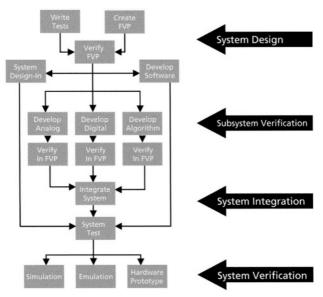

Project managers have often described the design and verification of hardware or software as a "V" process, as shown in Figure 5. In a V process, the project moves from design at a higher system level to design at lower chip to the block levels. The design is then integrated, then verified and tested from the low block levels back up to the chip and system levels.

Figure 5. Basic V Design and Test Process

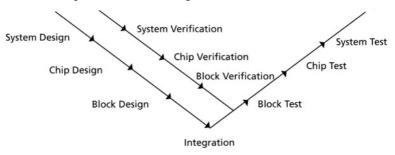

Advanced verification teams follow a modified V process. In the basic V process, the verification tasks include developing testbenches, writing tests, and running and debugging the tests. All of these tasks wait until integration is completed and follow in a linear fashion. Advanced verification teams accomplish the development of testbenches and tests in parallel with the design so that all that is left to do after integration is run the tests and debug. This modified V process is shown Figure 6.

Figure 6. Modified V Design and Test Process

In addition to decreasing the total project time, a separate verification process improves the quality of the results. Verifying a design often requires a different mindset than implementation. When you implement a design, you concentrate on how the design should work. When you verify the design, you also concentrate on how the design might not work. It is common practice in many software development processes that the designer should never be responsible for testing one's own code, because if the designer made an incorrect assumption or interpreted a specification incorrectly when implementing the design, the same assumption or incorrect interpretation will be made in testing the design. Having an independent person verify the design decreases the likelihood that the same incorrect assumptions or interpretations are made

in the verification. Engineers working solely on design verification provide an independent and focused approach that will find more bugs and find them faster.

Separating design and verification affects the organization and makeup of the development team. A complex project might require a large team of dedicated verification engineers who need a separate manager or lead to coordinate them and track their progress. Some teams might separate engineers into different groups focused on either design or verification. Other teams might have a single group of engineers and designate some as focused on design and some as focused on verification. Either way, the responsibilities for design and verification are separated, and the overall effect to the organization is the segmentation of verification engineers and the need for separate coordination of the verification process. Separating design and verification has affected the engineering community by providing a new area of specialization and a career path in functional verification.

### COORDINATING VERIFICATION WITH OTHER DEVELOPMENT TASKS

For many teams, functional verification is considered independent of other development tasks, such as architecture, software development, or system design-in. In actuality, there is great overlap between each of these areas and functional verification. Architects do not simply create new systems by pulling ideas from thin air. They often need to prove that their ideas are feasible or choose between different ideas. The process of testing feasibility and comparing system responses is very similar to a functional verification process. In many systems today, a large amount of the functionality of the product is encompassed in the software that runs the design. Verifying that the software works with the hardware is an important part of the verification of these systems. System design-in is the process of taking a device and implementing it in a final product. System design-in teams need to verify that not only is the device functioning correctly but that it will also function correctly in the final product.

Development teams that do not understand and manage the coordination of functional verification with other development groups waste time and resources. A common thread among functional verification, architecture development, software development, and system design-in is the need for a representation of the design: architects to test new ideas or algorithms; software developers to test that the software works correctly; system design-in teams to verify that the system works together; and verification teams to ver-

ify the implementation. When each of these groups works independently, the work required to create and maintain these representations is duplicated. If teams coordinate or reuse the functional representations, they can greatly reduce development time and resources.

In the past, teams could wait for a complete architectural analysis to be completed before beginning implementation, and software development could wait until the hardware had been designed. But if teams want to meet today's reduced development schedules, they must perform these development processes in parallel. This means that design and functional verification begins before the architectural analysis is completed. Software development is done in parallel with hardware development, and the final system design-in begins before all the parts are fully tested and working in the lab. Starting these development processes earlier in the project creates new demands for functional verification teams. The verification team begins with less well-defined architectural specifications and needs to combine performance testing with functional testing. The other development teams need a verified representation of the design earlier in the project, so the verification team must prioritize their efforts and synchronize with other development teams.

Closer coordination between the verification team and the other development teams affects the communication and scheduling of the verification process. Functional verification is often not considered until after the project has begun and progressed for a period of time. The thinking of many design teams was that the verification team should not engage on a project until the architecture and specification were complete and the design was well underway. If the verification team is to coordinate with the other development teams, it needs to engage in the project sooner. Verification needs to understand the development of the architecture if it is to help with performance analysis and if specifications are limited. Verification managers or leads also need to understand the requirements for deliverables between each group and to schedule resources accordingly. Organizationally, the verification team plays more of a central role in the development process.

#### VERIFICATION AS A MULTITHREADED PROCESS

Verifying simple small designs is a serial process. The verification effort is usually accomplished with basic simulation done on the entire device all at once or in a few small parts. There are few milestones to track or parallel processes to coordinate. But as designs grow larger, teams need to break the designs into hierarchical pieces to be tested independently before being integrated. As designs become more complex, different methods and techniques

need to be used to verify the design in different ways. Verifying a large complex design includes several parallel processes, multiple stages, and many dependencies to manage.

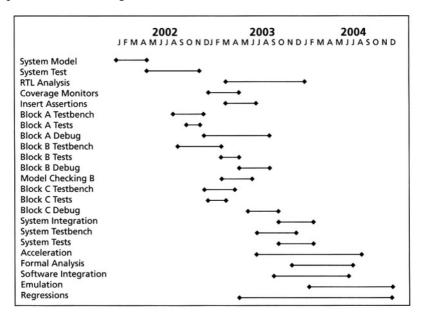

Figure 7. Verification Process with Many Tasks and Dependencies

If a complex verification project is not well managed, time is wasted and the quality of the results might be poor. A large verification project may consist of many environments to test the individual blocks, integrated subsystems, and final system. Each of these might have multiple dependencies, such as delivery of RTL, creation of testbench components, and creation of tests. If these dependencies are not managed well, engineers are stalled and unable to complete their tasks. The verification of a complex design can include multiple methods. The team might use simulation, static verification, emulation, and software coverification to verify different aspects of the same design. Managing the requirements of these methods so that each can be performed successfully improves the overall quality of the design.

A complex multithreaded verification process needs project management. A verification strategy must be developed early in the project to coordinate the multiple processes. A verification manager needs to be able to track the internal dependencies of the process as well as the status of the design and other development groups. Managing multiple dependencies requires a flexible verification team that is able to adapt to the inevitable events that shift priorities, resources, or schedules. The verification manager or lead needs to

have project management skills and understand the entire development process to be successful.

#### VERIFICATION IS NOT 100 PERCENT

Verification of small designs relies on the ability to completely verify the design. In the most basic verification approach, the design is stimulated with every possible combination of stimulus and the responses are verified to be correct. As the design size and complexity grow, it quickly becomes impossible to test every possible stimulus combination. One approach is to limit the testing by running suites of stimulus that stimulate the exact scenarios the design is intended to operate under. This can only be done for designs that operate in a confined deterministic manner.

If the size and complexity reach a point where it is impossible to verify every possible scenario, the verification team needs to develop a new strategy to be able to meet the schedule and avoid bugs slipping through the process into silicon. Some verification teams prioritize the possible scenarios and make sure that the most important scenarios are tested first. This approach reduces the chances of a bug being found in an important area of the design. Some verification teams use automation and random testing to verify as much of the design as possible in the allotted time. This provides the widest possible coverage that a bug does not exist. Most verification teams use a combined approach of running the most important scenarios first and then using random testing to cover the widest areas later in the process. Whichever method is chosen, the most important thing is to choose a strategy that addresses the project's needs.

Being unable to verify the design completely affects the entire development process. Developing a new design is an exercise in risk management. The verification team cannot provide 100 percent confidence that the design is functionally correct. There is always some risk of a bug slipping through the process and being found in the lab or at the customer. The more effort and time applied to verifying a new design, the less risk of a missed bug. The management team needs to decide when enough verification has been done so that the risk of a missed bug affecting the design is acceptable. There are many factors that go into this decision, including time-to-market pressure, development costs, and quality concerns. The verification team can assist this process by tracking progress closely and providing metrics to help measure the risk.

## VERIFICATION IS METHODOLOGY-BASED NOT TOOL-BASED

Today, standard verification is mostly done with simulation. As the design size and complexity grow along with the time-to-market pressures, development teams attempt to address perceived weaknesses in their verification with different approaches, such as assertion-based, transaction-based, or coverage-based verification. Each of these methods focuses on one or two individual verification issues, such as debug time or identifying coverage holes. Unfortunately, verification teams often find that when they base their verification on one method, it addresses the one issue but exacerbates others. Teams begin to add one tool or method after the other hoping to address their verification problems, but quickly find that due to incompatible tools and approaches they are spending more time addressing tool issues and less time verifying the design.

Verification tools associated with methods, such as simulation, assertions, coverage, or emulation, should not be the center of functional verification. These tools should be viewed as a collection of utilities to help reach your functional verification goals. A carpenter keeps a tool box full of different tools, but does not let the tools dictate how something is built or fixed. Instead, the carpenter figures out how to build or fix something and then chooses the right tools in the right sequence for accomplishing the task. In a similar manner, an advanced verification team needs to first understand what it is they are trying to accomplish, then develop a methodology using the right tools at the right time. In some projects, certain tools may be heavily utilized and, in others, they may be lightly utilized or not used at all. Functional verification becomes based more on the methodology used to reach the final goal than on the individual tools that may be used within the methodology.

Methodology-based verification places more emphasis on planning and strategy and less on techniques. Verification teams are often engaged late in the process and have no time to plan or develop a methodology. Thus, the methodology is developed on the fly, addressing whatever the most urgent issue is at the time. This leads to duplicated processes, wasted time, and poor results. When a team moves to methodology-based verification, they assess the needs of a project, plan how they will meet their goals, and develop the best approach for reaching their goals. Once a methodology is developed, the tools are brought together in a unified manner to address the project goals.

#### VERIFICATION DIFFERS FOR EACH DESIGN

The key to becoming a successful development team is not just the ability to develop one great product, it is the ability to develop multiple products. In the past, product life cycles were long enough that a development team could focus on one unique product at a time. In addition, most designs were very homogeneous—different functions, such as analog, algorithmic, digital, or radio frequency (RF), were developed independently on different devices. This meant that development and verification approaches from chip to chip were very similar. Today's product life cycles have decreased to the point that a development team may be finishing one design while they are working on the derivative design as well as the next generation. Designs are also now more heterogeneous with system on chips (SoC) containing multiple functions in the same device. The verification approach that worked for one chip may not work for the next.

Verification teams today need to evaluate each project before executing a strategy. Teams need to be able to adapt to different design types, different schedules, and different amounts of available resources. Two designs can be almost identical, but if the amount of resources or time available to verify is different, different strategies may be called for. This does not mean that every project requires a completely different strategy, but advanced verification teams need to be flexible to adapt to different circumstances while still keeping the same basic focus.

Verifying multiple designs has many implications. First, the verification team needs to accurately assess the needs of an individual team and plan a strategy to meet these goals. Teams cannot take a one-size-fits-all approach to a new project. A verification team also needs to develop a flexible and reusable verification methodology and supporting environment. Creating an environment that is flexible enough to support multiple projects with different needs takes more effort and time than creating an environment specific to one design. Management needs to understand the long-term benefits of developing a flexible environment and not push for short-term gains by cutting corners. The team needs to develop an environment based on open standards. Closed proprietary solutions might be the quickest solution for one project, but they are not expandable or adaptable. Open standards allow the environment to grow and adapt with changing needs.

There are many more characteristics of advanced functional verification, and there will always be new ones evolving. This book focuses on the techniques and processes currently used by teams throughout the industry. We will now look at how some of the successful teams employ the best practices of advanced functional verification to achieve their goals.

## Chapter 4

#### **Successful Verification**

Managing time and resources using advanced functional verification

By studying a number of successful advanced verification teams, a set of common guiding principles emerge. These principles guide how teams perform the process of verification as well as manage their time and use their resources. Throughout this book we present best practices used by advanced verification teams that can all be traced back to these common guiding principles.

#### TIME MANAGEMENT

Time management is an important part of any complex process. With proper time management, verification teams can complete verification sooner or perform more verification in the allotted time.

## **Start Early**

Every development project is unique and often requires new approaches for functional verification. Starting the process of verification early in the project enables the team to plan for new approaches and to adapt to changing environments. Starting early also allows verification to guide important early decisions, such as IP selection and feature support. As verification becomes a larger and larger portion of the development process, more decisions will need to be made to weigh the trade-offs and effects.

Functional verification requires preparation. If the verification team waits until the design has been implemented to begin, time is wasted developing and debugging the verification environment and tests. Verification teams need to be ready to test the implementation before it is received so that no time is lost.

Successful verification teams start by demonstrating the value of having verification knowledge early in the process. These teams become involved in the development and testing of system models used by architects and system designers. They also try to decouple the development of verification environments and tests from the implementation process so that they can be done in parallel. Of course, it is impossible for teams to engage in new projects early

if they are still supporting older existing processes. Successful verification teams are careful to stage the roll-off of verification resources from past projects to synchronize with the early needs of new projects.

## **Remove Dependencies**

The time it takes to complete a complex process like functional verification can be reduced by speeding the individual subtasks of the process or by removing the dependencies associated with the subtasks. Successful verification teams understand that time spent waiting for a deliverable from one task to start another task is wasted time. Removing dependencies not only decreases the amount of time to complete the overall project, it also uses the resources more efficiently throughout the project. Waiting for deliverables like HDL code or specifications leads to large spikes in resource utilization, followed by lulls as the resources wait for the next key deliverable.

Removing dependencies from external teams that are waiting for deliverables from the verification team reduces project time and improves the perception of the verification team. Implementation teams must wait for a bug-free design, and software teams often wait for functional models before beginning implementation. Staying off the critical path for the project should be an important goal of any verification team.

Successful verification teams remove dependencies in a number of ways. Many teams develop their own high-level system model to use in place of the HDL for developing tests and environments. The same system models can also be used as an executable specification, alleviating the need to wait for a functional specification. External dependencies can be met by providing the high-level model or an early prototype or emulation system to software and system design teams.

#### **Focus on Total Verification Time**

It is important to not lose focus on the big picture when concentrating on speeding up the individual processes and removing the dependencies in the verification process. Total verification time is the amount of time it takes from the start of the project until the design is declared functionally correct. Successful verification teams are aware of the larger project goals and adapt their plans and approaches to these goals. This allows these teams to use the appropriate processes and correct resources throughout the project to attain the project goals.

During a verification process, a team faces many trade-offs. When weighing trade-offs, you should always consider the effect on the total verification time and not simply the short-term milestone. When considering a new

approach or technique, successful teams measure the run-time improvements, but also factor in the user time. Executing a test faster is only beneficial if it does not adversely affect the amount of time you have to spend setting up the test or interpreting the results.

Successful verification teams focus on finding the easy bugs in a design early in the fastest, most efficient manner. These teams understand the importance of finding the critical bugs that may result in redesign. They are aware that their most valuable commodity is designer time, because designers are often the only ones with the knowledge to debug a failure and make the appropriate fix. They want to utilize the designer's time in the most efficient manner possible.

#### RESOURCE USAGE

Managing resources within a verification process is not simply trying to optimize and do more verification with fewer resources. Resource management also includes building teams and environments that facilitate efficient high-quality verification.

#### **Plan and Document**

The planning process may be the most important and the most neglected part of functional verification. Creating a verification plan provides a process for developing the strategies and tactics that will be used on a project before it has begun. This planning provides a map for the team to use as guidance during the process and as a means to track progress. Successful teams often have mechanisms that automatically track test and development status to goals listed in the verification plan. Without a proper plan, verification teams are left in a reactionary position, often taking many wrong turns on their way to reaching the project goals.

Successful teams solidify the plans and processes by documenting them. Documentation provides a mechanism for communicating the internal and external expectations and deliverables to the group. This communication becomes more important as team members engage and disengage from the process. It enables existing team members and new team members to be on the same page throughout the project. Successful verification teams are also careful to not overload the process with documentation. These teams make concise documentation part of each deliverable, providing enough detail to track the process but not requiring unnecessary overhead.

#### **Build a Team**

The goal in building a successful verification team is to have a team whose total abilities are greater than the sum of its parts. Successful verification teams most often consist of individuals who have a common baseline knowledge of verification as well as specialized knowledge in specific areas. Each team member is familiar with basic test writing and debugging skills in addition to an in-depth knowledge in an area, such as software development, testbench development, scripting, or emulation.

Just as engineers learn the profession of verification through experience and mentoring, verification teams also are built through experience and benchmarking. As a team works together, it learns to utilize the individual skills to meet the goals in the most efficient manner. Successful teams also benchmark themselves against other teams and learn from the best practices of these teams.

Successful verification teams build a cohesive team by selecting the right members and keeping them together. These teams select members with a wide range of abilities and experience. The verification process has many complex tasks that require experienced individuals, and it has many basic tasks that can be performed by less-experienced members. Having a well-balanced team keeps everyone engaged in the process and provides a path for development. A trademark of many of the most successful teams is that they have worked together for many projects. Keeping a verification team together is often difficult, but the benefits are enormous.

## **Use Someone Skilled in Management**

Managing a process as complex as verification requires experienced project management skills and a well-qualified leader. Project management requires planning, negotiation, and monitoring—skills not often found in the most technically talented individuals. Yet, in many organizations, the manager or lead of a verification group got their position by being the most technically skilled individual. Successful teams separate the need for competent project management from the need for competent technical leadership. A competent verification project manager provides value to the entire development team and uses verification experience to make the right trade-offs. The manager also provides a voice for the verification team to make sure that their concerns are heard.

Most successful advanced verification teams have competent project management as well as technical leadership. While these teams may not have specific roles or titles for these individuals, there are always one or two members who know what is going on and are coordinating the efforts of the team.

Successful teams develop their project plans and schedules in coordination with the overall project and do not let the other groups dictate their work. Organizations today understand the need for verification leaders and are designating lead or management roles for these individuals.

#### VERIFICATION PROCESSES

The verification process is made up of many smaller separate processes and techniques. Each of these smaller processes has its own unique tools and methods. Selecting these tools and techniques carefully results in the most efficient overall process.

## **Choose the Right Tool for the Job**

Selecting the correct verification tool or method for a particular task is vital to maximizing the overall efficiency of the process. Using the correct tool at the correct time is a matter of understanding the needs of the task and the capabilities of the available tools. Many teams rely solely on the tools that they are most experienced with. Other teams try to always use the newest tool or technique to gain a competitive advantage. The truth is that no one approach can address all your problems. In some cases, using the tools that you are most familiar with is the most efficient course, and in other cases new tools are called for.

Selecting the correct tools can save a team more than just time and effort. Verification tools can be quite costly. Some teams believe it is cheaper to buy only a few types of verification tools rather than a wide range. Teams should factor in the cost of the total quantity of tools and not allow themselves to get tied into one approach or tool. Verification tool vendors have moved from providing individual point tools to offering platforms of tools. These platforms reduce the overall cost of verification and also give verification teams the flexibility to select the correct tool for their job.

Successful verification teams select the correct tool for a job by first evaluating the needs of the task. Simulation is often a trade-off between speed and control. Fast simulators, such as hardware simulators, have the best performance but often provide poor visibility and control for debug. Software simulators have excellent control and visibility but at slow speeds. Successful teams use lower performance simulation during the early stages of debug when bugs are plentiful and switch to hardware simulators when simulations require long run times. Many teams rely solely on simulation for their verification, but some bugs, such as clock domain crossing bugs, cannot be simulated easily. Successful verification teams realize these bugs can be

detected faster with less effort with dedicated static tools. These are just a few of the possible trade-offs teams should make.

## **Choose the Right Information for the Job**

Verification tasks require more than just tools; they require accurate and efficient use of design information. The most basic trade-off verification teams need to make is between the speed of a test and the fidelity of its results. Simulations can be performed at very high speeds but provide results that are not specific enough to be useful. Simulations can be performed with great amounts of detail but take a long time to complete. Choosing the right balance of detail and speed is vital for maximizing overall verification efficiency.

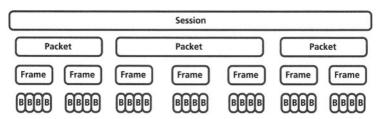

Design information is more than just the functional representation of the design. Input stimulus and output responses also characterize the design. Choosing the correct level of detail for this information facilitates the reuse of verification components within the testbench and eases test development. Choosing the correct level of detail for collecting coverage information and waveform data eases the collation and use of this data for debug.

Successful verification teams select the correct levels of information for the design representation and verification data at the beginning of the process. These teams might use a transaction-level model of the design to perform early performance and architectural analysis, which requires high speeds but only basic levels of detail. Later these teams use an RTL or gate-level representation of the design to verify the actual implementation details. Successful verification testbenches are often based on a common API that facilitates reusing components written with a common level of detail. Using these testbenches, along with common databases, facilitates the fastest, most efficient test and debug processes.

#### **Automate**

Automating the various tasks of the verification process reduces the time and effort the team spends on repetitive tasks. The verification process contains many individual tasks that might be repeated hundreds or thousands of times during a project. Automating these tasks might not speed up the individual task, but it does free up valuable resources to concentrate on other tasks. Resource loads can be balanced to utilize the available resources, such as computers and software licenses. Automation can also facilitate higher quality results. Human error can easily enter long repetitive tasks, such as running large test suites and collecting results. Removing the chance of human error assures more consistent reliable results.

Automation also helps in documenting the verification process. Proper scripting of the various verification tasks provides a verification record. These scripts can be used to understand the process if the project needs to be redone or modified at a later date.

Successful verification teams automate every chance they get. Any process that is performed more than a few times is automated. The most common automated verification tasks are building, compiling, and executing simulations. By the time a large project nears completion, a simulation regression environment can contain thousands of tests that need to be run and rerun with each change in the design or environment. Maintaining the integrity of the model as it nears tapeout becomes mandatory. As time moves on, parts of older projects are often incorporated into newer projects as IP. Automating the verification environment facilitates this process, making it easy for the new project to integrate and test the older code.

#### **APPROACHES**

Proper management of time, resources, and tools results in a highly efficient advanced verification process. The last group of principles encompasses the overall verification approaches that successful verification teams use.

## **Keep Verification Real**

The closer the verification of a design reflects the design's real operating environment the better the quality of verification. It may seem obvious that verification teams should strive to create test environments and stimulus that reflect the real-world conditions the design will face. But many verification teams get caught up in developing complex testbenches and using complex formal techniques and lose the big picture. The goal of verification, and of the entire development process, is to produce a product that works as intended. This goal not only keeps the verification "real," it is also more efficient. It is impossible to verify everything in a large complex IC. Teams must prioritize, and the highest priority should be what is most important to the end product.

Another benefit of keeping verification real is that it becomes easier to understand. Test writers and debuggers can more easily comprehend their task if it can be related to a real application. Humans naturally think in terms of concrete concepts, such as real images or communications. Using verification environments that allow engineers to conceptualize what they are working on makes verification easier and more efficient.

Successful verification teams develop environments that reflect the real world whenever possible. These teams utilize input data such as images, pro-

gram streams, or traffic flows taken directly from real-world applications. The teams also utilize tools, such as emulators that allow the design to be tested in a real-world environment. This extra verification not only verifies that the design works correctly, but also verifies that the testbench and models that were used are correct for future use. Finally, these teams write their environments so that tests can be written at a higher application level and results can be debugged at that same high level. Transactors or adapters are written to translate between these higher level data abstractions, such as an image or a packet, down to the signal level necessary for detailed verification.

## **Stress the Design**